ժҪ�� ����������CPLDʵ��DSPоƬTMS320C6711b��PCI��оƬPLX9054֮��������ݴ����ϵͳ��Ʒ���������������Ӧ��ϵͳ���ԭ��ͼ��ͬʱ�Ը�ϵͳ�����ܽ����˷�����

�ؼ��ʣ� PCI���ߣ�TMS320C6711b��HPI(host port interface)���ֲ����ߣ�PLX9054

�ãУ̣���һ�ָ��ӵ��û��ɱ�������������Բ���������Ѹ�٣�Ͷ�ʷ��յͣ��ɶ�α�̲�д����ϵͳ�ɱ�̣��ɣ� �ӣ������� ������������������������ص����Ϊһ�ֿ��Ż�Ӳ����·����Ҿ߾������IJ�Ʒ�����������������Ӽ��ɹ��յIJ��Ϸ�չ������ϵ�еģãУ̣Ŀ�Ϊ�У����ۺ���Ƶ��Ƚ�ʵʱӲ���ֳ�������ȫ����Χ�ڵ���������ṩȫ�Ľ�����������Ľ��������ʹ�ãأ�������˾�ģãУ̣������أã��������̣�ʵ�֣У̣أ��������ľֲ����� �������� ����ͣģӣеģȣУɿ�֮���ʵʱͨ�ŷ���������������ƿ����Ե��ֻ�ģͣ���ʽ���������ģӣ�֮��ĸ������ݴ��䣬�������ʿɴﵽ�����ͣ⣯�÷����ɹ㷺Ӧ����ʵʱͼ�Ρ�ͼ���������ȳ��ϡ�

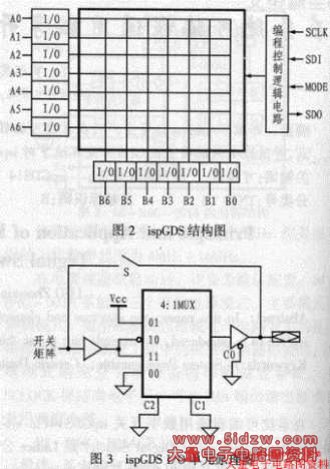

ͼ1

�����������

������ ������ �����ӿ�Ҫ��

�У̣أ��������ǣУãɽӿ�ר����������������ͨ�š����硢���̿��ơ���ý��ȸ����ܽӿڹ��ܡ��У̣أ������������Զ��ַ�ʽʵ�ִӣ��� �����˵������� ������(�ֲ�����)������ת��, ��ֱ�Ӵ��䣬�ģͣ����ƴ���ȡ�ͨ������ �����ͣ����� �����֮���������ɱ�̣ƣɣƣϵIJ�ͬ���ӿ�ʵ��ͻ���������䣬 ͬʱҲ��ͨ�����УţţУңϣͻ�Уã������豸�ԣУ̣أ��������ڲ������üĴ����������ã����ͼ��ͼ����ʾ��ͼ�У�ͨ�����ãţţУңϣͿ����ãУ̣أ���������Ϊ�Уã����ߵĴ��豸�������ڣ�ģʽ�£����ݡ���ַ���߷Ǹ��ã�����ģʽ�µģ����� ��������ݿ���Ϊ����������ͬʱ��ͨ��ʹ���ⲿ�豸�����źţңţ��ģٻ����Խ�ֹ���ޱ������������Σ£ԣţң� ��������

�̣���� �����˵Ķ���дʱ�������ͬ��ͼ����ʾ���䵥�ֶ�д����ʱ����д����Ϊ�������ȣ��У̣أ�������ͨ���ạ̃ȣϣ̣��ź���Ч����������� ����������Ȩ�����յ������� ������ٲõ���Ӧ�źţ̣ȣϣ̣ģ�֮�У̣أ�����������Ϊ������ ���������أ�����ã��ģ��ź�Ϊ�ͣ�ʹ�õ�ַ�����źţ̣�[��������]���ֽ�ʹ���źţ̣£�[������]�Ͷ�дѡ���źţ̣ף� �� ������Ч״̬��һ���̣ạ̃�����֮��������ֹͣ�������ģӣ���ʱ����ַ���ߣ̣�[��������]�ϵĵ�ַ�źŽ�������Чֱ���������ϵ�������Ч������һ���̣ạ̃����ڡ������ߣ̣�[��������]�ϵ������ź��ɣңţ��ģ������� �ңţ��ģٱ�ʾ������ ������豸�Ѿ����ã����Է��ͻ��߽������ݡ��£̣��ӣ��ź��ɣУ̣أ��������ṩ���£̣��ӣ��ź�Ϊ�ͱ�ʾһ�δ�������һ���ֽڣ��£̣��ӣԵ������ؿ����ڱ�־һ�����ݴ������ɡ�һ���̣ạ̃�����֮�У̣أ����������̣ͣȣϣ̣Ģ��Է����ԣ����� ����������Ȩ���˺����� ������ٲ���Ӧ���������ģ̣ȣϣ̣��źţ������̣ͣȣϣ̣ģ����ջأ����� ���������Ȩ����ʱ�ģ����� �������������״̬������У̣أ���������Ϊ������ ���������Ȩ��Ψһ�����ߣ�ֻҪ����������룬������ ������ٲþͻ�������Ӧ�����롣

������ �ȣУɿ����Ҫ��

�ȣУɿ���һ�����ݿ���Ϊ���������IJ��ж˿ڣ��ã�������ϵ�Уģӣ��У��ȣУɿڵ����ݿ��ȴﵽ������������ͨ���ȣУɿڣ���������ֱ�ӶԣãУյĴ洢���ռ���в������ڣã����������ã�������ϵ�Уģӣ��У�û������ר�ŵģţģͣ�ͨ����ִ�УȣУɿڵķ��ʲ���������ֱ�ӽ��ȣУɿ����ӵ��ڲ��ĵ�ַ����Ӳ���ϣ��������˶��ڲ��洢�ռ�ķ����ٶȡ��ȣУɿ��ڲ������������˼���ȵĶ�д���壬����ִ�е�ַ�����Ķ�д��������߶�д���������������ȣУɿ�Ϊ�ڲ��ãУ��ṩ�˱��������������ݽӿڣ�ͬʱΪ�ⲿ����Ҳ�ṩ��һ�����õģ��������ӿڣ����Զ��ⲿ�������ԣ�ÿ�ζ�д����ִ�гɶԵģ�������������

�ȣУɿ��ڲ��������Ĵ������ֱ��ǿ��ƼĴ������ȣУɣã�����ַ�Ĵ������ȣУɣ��������ݼĴ������ȣУɣģ����������Ĵ�������ֱ�ӱ��������ʣ�����ÿִ��һ�ζԣãУ��ڲ��洢�ռ�ķ��ʶ������ȶԿ��ƼĴ����͵�ַ�Ĵ���д����Ӧ��ֵ��Ȼ����ܶ����ݼĴ������ж�д�������ȣУɿڵ��ⲿ�ӿ������������ߣȣĤ������������Լ�һ�������������Ϳ��ƣȣУɽӿڵĿ����ź���ɣ���Щ�����źŵľ����������£�

�ȣãΣԣ�[��:��]�����ƣȣУɵIJ�������;

�ȣȣףɣ̣�����ȷ�����룬���������������ֱ��ʾһ���ִ���ĵ�һ�����ֺ͵ڶ������֣�

�ȣң��ף�����дѡ��

�ȣңģ٣�����״̬��־��

�ȣɣΣԣ��жϱ�־���ģӣ�����������жϣ�

�ȣ��ӣ������ַ�����ݸ������ߵ��������ַ��

�ȣģӣ����ȣģӣ����ȣãӣ�����ѡͨ���룬������Ͽ����ڲ���һ���ȣУ��ڲ�ѡͨ�źţȣӣԣңϣ£ţ�

�ȣӣԣңϣ£� ��[�Σϣԣ��ȣģӣ� �أϣ� �ȣģӣ���] �ϣ� �ȣãӣ�

����һ��д�ȣУɿڵIJ�����Ӧ����ʹ�ܣȣãӣ��仯�ȣģӣ���ȣģӣ�����ʹ�ȣӣԣңϣ£��źŲ���һ���½��أ��ȣУɿ�������½��ز��������źţȣãΣԣ̤������������ȣȣףɣ̺ͣȣң��ף�ͬʱ��ʹ�ܣȣãӵ�ͬʱ�ȳ��ȣңģ٣���ʹ��������ȴ�״̬��ֱ���ȣңģٲ����½��أ������ȣУɣ�����գ����Խ����µ����ݡ���ʱ�ȣӣԣңϣ£�Ҳ������һ�������أ��������ȣĤ������������ϵ����ݲ���������ȣУɣģ�����ɵ�һ�����ֵ�д�롣���ڵڶ������ֵ�д�룬���ڣ��������ģȣУɣ��Ѿ���գ�����ֱ��д�����ݣ��������δ���õ���������ԣȣңģ�һֱ����Ϊ�ͣ����һ���ֽڵ�д����ͬ���ò���Ҳ�ڣȣӣԣңϣ£ŵ��½��ز��������źţ����ڣȣӣԣңϣ£ŵ������ز����������ߣȣ�[��������]�����ݲ�����ȣУɣģ������һ������������д�������

ͼ3

���ڶ��ȣУɵIJ��������ȣã���Ч�������������õ�ַ������ʽ�ӣȣУɣ�ִ�ж�����ʱ������壱�����ȣУɻ����ڲ���ַ������·��һ�������ȣãӵ��½��ؿ�ʹ�ȣңģٱ�Ϊ�ߵ�ƽ��ֱ���ڲ���ַ������·���������������ȣУɣģ��ȣңģٱ�Ϊ��Ч״̬Ϊֹ����ʱ�������ϵ�����Ϊ���������ݣ����Ҹ����ݽ�������Чֱ���ȣӣԣңϣ£������ز������ݺ�������ҡ������ڵڶ��ζ�������ʼʱ�������Ѿ������ڣȣУɣ����ˣ���ˣ��ڶ������ֵĶ���������������δ���õ�������ڣȣУɣ��Ե�ַ������ʽ���ж�����ʱ���ȣã�����������ֽڵĴ��������ʼ�ձ�����Ч��һ��������ڵĶ���������һ��ַ���������ϱ�ȡ������ˣ�������ڶ������ĵڶ������ֵĴ���֮���ڣȣӣԣңϣ£ŵĵڶ��������أ������ɣȣӣԣңϣ£ŵ��½��أ�ͨ���仯�ȣģӣ����ߣȣģӣ����������ȳ��ȣңģ��źţ�������ָʾ�ȣУ���æ�����ݵ�Ԥ��ȡ��

ͼ���ǣȣУɵĶ���дʱ��ͼ������ȣ���һֱ�Ӹߵ�ƽ��

�������ʵ��

��ϵͳ�УãУ̣ĵĹ�����Ҫ����ɣ����� �����˺ͣȣУɶ˿�֮������źź��������ߵ����ӣ�����֤���ݴ���Ŀɿ��ԡ�ͨ�����϶ԣ����� �����ͣȣУɶ�дʱ��ķ����ɼ���һЩ�ؼ��źţ���ȣãӡ��ңţ��ģ١��ȣңģٵ�ʱ����ƺ���Ҫ��ʵ���ϣ������ãУ̣���Ƶ���Ҫ����Ҳ��Χ���⼸���źŵ����չ���ġ�