摘 要:在FPGA开发的各个阶段,市场为我们提供了很多优秀的EDA工具。面对眼花缭乱的EDA工具,如何充分利用各种工具的特点,并规划好各种工具的协同使用,对FPGA开发极其重要。本文将通过开发实例“带顺序选择和奇偶检验的串并数据转换接口”来介绍基于多种EDA工具――QuartusII、FPGA CompilerII、Modelsim――的FPGA协同设计。

关键词:FPGA;EDA;协同设计

一、前言

FPGA在电子市场上占有举足轻重的地位。现在的问题是:现在市场在FPGA开发方面的EDA工具令人眼花缭乱,各自侧重点不同,性能也不一样,我们应该如何选择?为了加速FPGA的开发,选择并协调好各种EDA工具显得非常重要,本文将探讨上述问题并给出一种解决方案。本文以Altera公司的FPGA为目标器件,通过开发实例介绍FPGA开发的完整的流程及开发过程中使用到的开发工具,包括QuartusII、FPGA CompilerII、Modelsim,并重点解说如何使用这三个工具进行协同设计。

二、FPGA的开发流程及实例

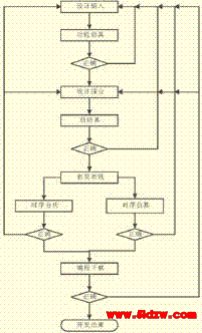

FPGA的开发分为设计输入、功能仿真、设计综合、前仿真、布局布线、时序仿真、时序分析和编程下载几个步骤。设计流程如图1所示。

我们的开发实例是“带顺序选择和奇偶检验的串并数据转换接口”。接口电路可以实现数据的串并转换,并根据控制信号确定输出的并行数据的顺序,以及输出奇偶检验位。开发实例是用来说明FPGA的开发流程和各种EDA工具的协同设计,因此这里的描述重点并在设计本身。开发实例使用的目标器件是Altera公司FLEX10KE系列的EPF10K30ETC114-1;开发软件有QuartusII2.0、FPGA CompilerII 3.6和Modelsim5.6SE。

Quartus II是Altera公司的第四代可编程逻辑器件集成开发环境,提供从设计输入到器件编程的全部功能。 Quartus II可以产生并识别EDIF网表文件、VHDL网表文件和Verilog HDL网表文件,为其他EDA工具提供了方便的接口;可以在Quartus II集成环境中自动运行其他EDA工具。

Mentor Graphics公司的Modelsim是业界较好的仿真工具,其仿真功能强大,且图形化界面友好,而且具有结构、信号、波形、进程、数据流等窗口。

FPGA Compiler II是一个完善的FPGA逻辑分析、综合和优化工具,它从HDL形式未优化的网表中产生优化的网表文件,包括分析、综合和优化三个步骤。

如果设计的硬件系统不是很大,对综合和仿真的要求不是很高,我们完全可以在Quartus II中完成设计。实际上,这个开发实例完全可以在Quartus II这个集成的开发环境中完成。下面,我先介绍一下如何在Quartus II中完成设计,然后再介绍如何利用Quartus II提供的第三方EDA工具的接口与其他EDA工具(包括综合工具FPGA Compiler II和仿真工具ModelSim5.6SE)完成协同设计。

1. 基于Quartus II的FPGA的开发

利用Quartus II软件的开发流程可概括为以下几步:设计输入、设计编译、设计时序分析、设计仿真和器件编程。

(1)设计输入

Quartus II软件在File菜单中提供“New Project Wizard...”向导,引导设计者完成项目的创建。当设计者需要向项目中添加新的VHDL文件时,可以通过“New”选项选择添加。在这里我们创建项目“s_to_p”,编写“s_to_p.vhd文件”,并将文件添加到项目中。

(2)设计编译

Quartus II编译器完成的功能有:检查设计错误、对逻辑进行综合、提取定时信息、在指定的Altera系列器件中进行适配分割,产生的输出文件将用于设计仿真、定时分析及器件编程。

①首先确定软件处于Compile Mode,可以通过Processing菜单进行选择。

②在Processing菜单中选择Compiler Settings项。在这里可以进行器件选择、模式设定、综合和适配选项设定及设计验证等。我们选择FLEX10KE系列型号为EPF10K30ETC114-1的器件,并选择在编译后进行时序分析。

③单击Processing菜单下的“Start Compilation”项,开始编译过程。

④查看编译结果。编译结果以树状结构组织在Compilation Report中,包含项目的设置信息,以及编译设置、编译效果等信息,同时也包含了静态时序信息。

(3)设计定时分析

单击Project菜单下的“Timing Settings...”选项,可以方便地完成时间参数的设定。Quartus II软件的时序分析功能在编译过程结束之后自动运行,并在编译报告的Timing Analyses文件夹中显示。其中我们可以得到最高频率fmax、输入寄存器的建立时间tsu、输出寄存器时钟到输出的延迟tco和输入保持时间th等时间参数的详细报告,从中可以清楚地判定是否达到系统的时序要求。本设计实例电路的fmax可达到192.31MHz。

(4)设计仿真

Quartus II软件允许设计者使用基于文本的向量文件(.vec)作为仿真器的激励,也可以在Quartus II软件的波形编辑器中产生向量波形文件(.vwf)作为仿真器的激励。通过Quartus II的波形编辑器,我们编辑波形文件“s_to_p.vwf”用于仿真。接着,在Processing菜单下选择“Simulate Mode”选项进入仿真模式,选择“Simulator Settings...”对话框进行仿真设置。在这里可以选择激励文件、仿真模式(功能仿真或时序仿真)等,我们选择时序仿真,单击“Run Simulator”即开始仿真过程。完成仿真后,我们可以通过时序仿真得到的波形判断系统设计是否达到要求。

(5)器件编程

设计者可以将配置数据通过MasterBlaster或ByteBlasterMV通信电缆下载到器件当中,通过被动串行(Passive Serial)配置模式或JTAG模式对器件进行配置编程,还可以在JTAG模式下给多个器件进行编程。利用Quartus II软件给器件编程或配置时,首先需要打开编程器(在New菜单选项中选择打开Chain Description File),在编程器中可以进行编程模式设置(Mode下拉框)、硬件配置(Programming Hardware对话框)及编程文件选择(Add File...按钮),将以上配置存盘产生.cdf文件,其中存储了器件的名称、器件的设计及硬件设置等编程信息。当以上过程正确无误后,单击Start按钮即可开始对器件进行编程配置。这里我们需要根据外围硬件电路设计的情况进行选择。

2.多种EDA工具协同设计

在FPGA设计的各个环节都有不同公司提供不同的EDA工具。每个EDA工具都有自己的特点。一般情况,由FPGA厂商提供的集成开发环境,如Quartus II,在设计综合和设计仿真环节都不是非常优秀,因此一般都会提供第三方EDA工具的接口,让用户更方便地利用其他EDA工具。在这方面,作为EDA集成开发环境的Quartus II做得很好,不仅可以产生并识别EDIF网表文件、VHDL网表文件和Verilog HDL网表文件,为其他EDA工具提供了方便的接口,而且可以在Quartus II集成环境中自动运行其他EDA工具。

在FPGA的开发中,如果选用Altera公司器件的话,Quartus II+FPGA Compiler II+Modelsim的工具组合是非常理想的选择。如图2所示,使用这三个EDA工具对实例进行协同设计的流程。下面,我们将详细介绍这三个工具的协同设计。

(1)设计输入和综合

在FPGA Compiler II中编辑“s_to_p.vhd”设计文件,并进行逻辑分析、综合和优化。使用FPGA Compiler II综合时,我们能够设置综合的各种约束条件及优化重点,并选择不同厂家的器件。在设计中,我们使用File菜单中的“Design Wizard”,创建项目,添加“s_to_p.vhd”设计文件,并选择Altera公司FLEX10KE系列型号为EPF10K30ETC114-1的器件为目标器件,在设置完成后,软件将自动开始综合和优化。综合、优化后,我们可以查看结果和综合所得到的原理图,看看是否能满足要求。接着,在Synthesis菜单中选择“Export Netlist...”打开导出网表的对话框。在这里,可以设置和导出用于布局布线和前仿真的网表。在项目对应的文件夹中,“s_to_p.edf”是用于Quartus II布局布线的,而“s_to_p.vhd”(注意:这个文件和源文件具有相同的名字)则用于Modelsim前仿真的。