ժҪ�������˳�����ͬ�����Ļ�������ԭ����������ڳ�����ͬ����������ģ�������ƻ�ý�С��λ�����ķ����������˳�����ͬ�����ڣƣУǣ��ϵľ���ʵ�֡�

�ؼ��ʣ�����ͬ�� ģ������ �ƣУǣ�

������ͨ��ϵͳ�У������Է������ʶԽ������������������Եز�����Ϊ�ˣ���������Ҫһ������ʱ���źţ����ʱ���źŵ�Ƶ�ʺͷ���������ȣ���λ����뱣֤����ʱ������ѵġ��ڽ������л���������ʱ�ӵĹ��̱���Ϊ����ͬ������Ŷ�ʱ�ָ��������ţ��ţ������������ �ǣ���壩��ʵ�ַ���ͬ������Ҫ����֮һ���㷺�����ڸ�������ͨ��ϵͳ�С���������Ļ���ģ�����Ƶij������봫ͳ�ij�������ȣ�����ͬ���ٶȿ졢����С����λ����С���ŵ㡣����ƣУǣ�ʵ���У�������������ʵʱ������Ƶķ����������ʵ��Ӧ�õ�����������Ʊ�ת��Ϊ�����̣���һ�����˵�·��

�� �����ż��

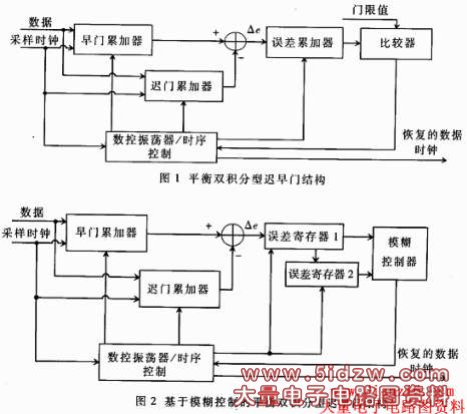

һ�ױջ�ƽ��˫�����ͳ����Žṹ��ͼ����ʾ��

�����ۼ����ͳ����ۼ����ֱ������������İ���������ڶ��������ݵIJ���ֵ�����ۼӣ�������ǰ��������ںͺ����������ڽ��յ����źŵ�������������һ����������ͬ��������λ�������Ϊ�˱�֤��λ������Ч�ԣ�����ʱ�ӵ�Ƶ�ʱ����Ƿ������ʵ�ż������һ������ҪΪ������������յ����ź�Ϊ�����ģ�����ô��λ����Ϊ�㣻������յ����ź��У�����������֣���ô��λ������ܲ�Ϊ�㡣����ۼ����ͱȽ���������һ��ͨ��·�˲�������λ����ۼ�ֵ��һ������ֵ�Ƚϣ������IJ�ֵ���Ʊ������ɵ�����ʱ����λ����λ����ۼ�ֵ�ķ��ž�������ʱ�ӵ���λ��ǰ�ƻ��Ǻ��ƣ�ÿ����λ�����ķ����ǹ̶��ģ�����������ֵҲ�ǹ̶��ġ����������ݱ������ɵ�����ʱ�Ӿ��������ۼ����������ۼ���������ۼ����Ĺ���ʱ��

�������ŵIJ�������Ϊ�ԣ����������ĵ�������Ϊ�䣬�����ڳ�������λ������ɵĽ�������ʱ�ӵ���λ����Ϊ�䡤�ԣ�����������ȣ�ϴ�������ʱ�ӿ��Ժܿ��ͬ���ϣ�������λ�����ͻ�Ƚϴ�����������ȣ��С������λ������С����������ʱ�ӿ�����Ҫ�ϳ���ʱ����ͬ����

�� �����ŵ�ģ���������

ͬ���ٶȺ���λ��������Լ���������ܵ�����ߵ���Ҫ���ء�Ϊ��ʵ�ֽ�С��λ����Ҫ���µĿ���ͬ�������Բ�������Ӧ����������λ����ʹ�ýϴ�ĵ������ȣ�����λ���ٽ�ʹ�ý�С�ĵ������ȡ����������һ�ֻ���ģ�����Ƶķ�����ͬ�����Դﵽ����Ӧ��Ч��������³���Ժá�����ʵ�֡�

����ģ�����Ƶ�ƽ��˫�����ͳ����Žṹ��ͼ����ʾ��

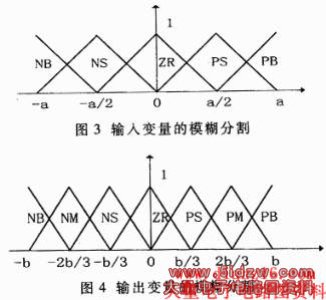

�ڽṹ�ϣ�����ģ�����Ƶij�������������λ���Ĵ���ȡ���˴�ͳ�����ŵ���λ����ۼ�������һ�������롢�������ģ��������ȡ���˴�ͳ�����ŵļȽ�������ģ��������������Ϊ��λ����ۼ�ֵ�ĵ�ǰֵ���壨���ǰһ�μ���ֵ���壨����������Ϊ���������ĵ�������ֵ�䡣�������������Ⱥ����������������ģ���ָ�Ϊ���Σ£�����С���Σӣ����㣨�ڣң�����С���Уӣ������У£�����ȡֵ��ģ���ָ��ͼ�α�ʾ��ͼ����ʾ����������䱻ģ���ָ�Ϊ���Σ£������У��Σͣ�����С���Σӣ����㣨�ڣң�����С���Уӣ������У��Уͣ������У£�����ȡֵ��ģ���ָ��ͼ�α�ʾ��ͼ����ʾ��

ģ���������Ŀ��ƹ�����������ʾ��

��1 ģ�����ƹ������λ��e(n-1)

| ���e(n) | DCO��������d | NB | NS | ZR | PS | PB |

| NB | PB | PB | PM | PM | PS | |

| NS | PB | PM | PM | PS | PS | |

| ZR | PM | PS | ZR | NS | NM | |

| PS | NS | NS | NM | NM | NB | |

| PB | NS | NM | NM | NB | NB |

����ģ���������������ģ���ָ����������ȡֵ���У������Ľ��������Գ�����㣨�������ᣯ�������ᣩ����ľ�ȷ����ֵ����Ӧ�������ƹ���ģ������������������������������ķ���

�� ģ�����Ƴ����ŵģƣУǣ�ʵ��

��ʵ�������У���Ҫ�Խ��յ��ģ��ͣ����˹��СƵ�Ƽ��أ��ǣ����ͣӣˣ��źŽ��з���ͬ�������Ҫ��ģ�����Ƶ�Ԫ�������ٶ�����Ϊ���� �ƣ̣ɣУӣ��ƣ������� �̣������ �ɣ��������� ���� �ӣ����䣠����Ȼ���������������ٶ�ָ�꣬��������һ���ͨ�ô��������Ǻ���ʵ�ֵġ���ˣ�ģ�����Ƴ����ű���ʹ��Ӳ����ʵ�֡��ƣУǣ���һ�����۵İ붨�ƴ��ģ���ɵ�·�����Ŀ������߿����ڣУû������С��ƣУǣ������ܶȸߡ��ṹ�����ʱ��̺Ϳɱ�̵��ŵ㣬�dz��ʺ�����ģ�������ŵ�Ӳ����֤��

һ�����͵�ģ��������ͨ���ɰ������ƹ����֪ʶ�⡢ģ��������Ԫ�Լ����ⲿ�ӿڵ�ģ������Ԫ����������Ԫ��ɡ��ԣ�������������������ģ����������Ӳ��ʵ�ַ����Ѿ����˺ܶ���������ֵ�·ʵ��ģ���������Ѿ��зdz��������Ʒ�������Щ������ģ�����������ĸ�������Ԫ�����ֵ�·һһʵ�֣�ģ�������ٶ�Ҳ���Դﵽ���� �ƣ̣ɣУ����ϡ�������ģ�����Ƴ������У�ģ��������ֻ�����е�һ���֣�������Ҳֻ���������ջ��е�һ����Ԫ���������ͨ�õ���Ʒ��������ʵ�ֵ�ģ�����Ƴ�����ռ�ãƣУǣ�������Ԫ��Ȼ�ܶ࣬��ʹ�������ջ�ռ�õ�оƬ����ܴ���ģ���������ڳ������еĹ��ܱȽϵ�һ����ʵ�ָ��á���ˣ�ģ�����Ƴ������е�ģ����������������ͨ������Ʒ�����Ϊ�˼�Сռ�õ�оƬ�����ģ�����������������µ����˼·�����ȣ�ȷ�����������ȷ���ı�������Ȼ��������ģ�����Ʊ��������һ�����������ȷ��֮�����ֵ�������������ֵ������Ϊ�����̡�������ģ���������Ϳ����ü��������ʵ�֡���������̺�����Ӳ���������Ա�д����Ȼ���ڣƣУǣ�����ϵͳ�жԱ�õij���������������������ֵij�����б��롣�������ɹ����ƣУǣ�����ϵͳ������һ���ƣУǣ�оƬ�������ļ�������������ļ�ͨ�����õ������ص�оƬ��������յõ�һ��ʵ��ģ�����Ƴ����ŵ�оƬ��

������ģ�����Ƶij�����ͬ��������FPGAʵ��