摘要:对用于单片机的键盘子系统的专用键盘接口芯片进行功能分析,就芯片中核心部件的时序设计进行状态描述,并利用可编程逻辑技术和原理输入方式对键盘接口芯片的内部结构加以实现。

关键词:键盘子系统 专用键盘接口 CPLD 状态描述

在单片机应用系统中,存在多种形式的外部数据输入接口界面,例如RS-232C串行通信、键盘输入等[1,4]。其中利用键盘接口输入数据,是实现现象实时调试、数据调整和控制最常用的方法。单片机的外围键盘扩展电路有多种实现方式,例如直接利用I/O接口线或外接8255A接口芯片,配合适当的接口管理程序,就可以实现外围键盘扩展功能。但是,在这些方法中,键盘扩展电路需要占用单片机的资源对按键进行监控和处理,这对要求高实时性处理的单片机系统是不实现的。为了解决这一问题,可以使用专用键盘接口芯片(例如Intel8279)[2]来组建键盘子系统。而且,这类专用键盘接口芯片在使用灵活性方面尚有欠缺,尤其当用户需要实现某些特定功能时,其缺点更为明显。针对上述问题,本文提出一种利用复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)设计技术[3]实现专用键盘接口芯片的方案。

1 系统原理

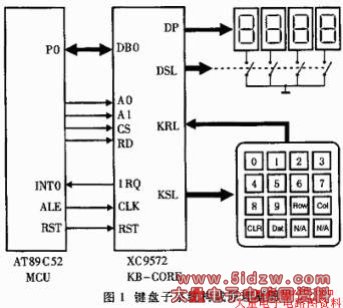

图1是单片机系统中键盘子系统的构成原理框图。其中键盘接口芯片KB-CORE是该子系统的核心部分,它应具备如下功能:第一,产生按键扫描时序,并进行硬件去抖动。如果直按键按下,实现按键编码、中断处理等功能。第二,可以区分处理数字键和功能键。数字键钭由接口芯片暂存,而当功能键被按下时申请CPU中断处理;对多个按键同时按下,按一定的编码优先级处理。第三,提供与MCS-51系列单片机兼容的接口,单片机可以读取芯片中保存的数据或功能代码。第四,提供数据显示接口,可以直接驱动4位七段LED数码管,并进行动态扫描显示。

按键根据键盘子系统的服务对象拟设置子数字键(0~9)、功能键(ROW、COL、DAT)、清零键(CLR)共14个,排成4×4的矩阵,有两个未定义。

2 专用键盘接口芯片功能结构设计

根据上述专用键盘芯片KB-CORE的功能要求,图2示出本芯片内部应有的结构框图。

其工作原理如下:(1)键盘扫描控制及编码电路中内含一个环形计数器。该计数器计数输出至KSL[0~3]端作为键盘扫描信号。每当扫描信号发生变化时,键盘扫描控制器从KRL[0~3]端读入某一行按键的状态信号。如果没有按键被按下,则扫描下一行;如果有按键被按下,则控制器锁定被扫描行,并延迟约10ms去抖动,然后再次扫描被锁定行以确定按键是否误读。如果按键被证实按下,则一直等待直至用户松开该键。与此同时,数字键码将被保存到先进先出存储器,功能键则直接产生中断请求信号IRQ,通知CPU读取键码DBO[0~7]。(2)FIFORAM中数据容量为16位。每4位对应一个字形符,所以七段LED数码管需要4位。(3)扫描发生器一方面产生LED的位选信号DSL[0~3],另一方面产生扫描显示输出控制电路的位数据选通信号。扫描显示输出控制电路根据位数据选通信号读取FIFO RAM中相对应的数据,然后送七段译码电路输出DP[0~6]驱动LED显示屏的段选信号电极。(4)接口控制电路一方面用来识别CPU的读时序;另一方面用来对地址信号线A1A0译码,实现对输出数据的选择。若A0A1=“00”,则输出FIFO RAM中的低字节数据;若A0A1=“01”,则输出FIFO RAM中的高字节数据;若A0A1=“10”,则输出控制数据(表明ROW、COL、DAT中哪一个被按下);若A0A1=“11”,则不输出FIFO RAM中的任何数据。

3 专用键盘接口芯片核心部分的状态描述与实现

为了实现上述专用键盘接口芯片功能结构,利用可编程逻辑技术对各个功能块进行逻辑的序描述和实现。由于键盘扫描控制和去抖的逻辑时序设计较复杂并具典型性,因此下面将对键盘扫描控制和去抖部分的设计思想进行介绍。

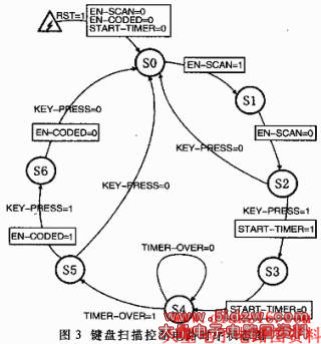

键盘扫描时序的基本原理[4]可能用图3所示的状态图表示。状态图的输入变量为RST(复位)、KEY-PRESS(有按键)、TIMER-OVER(去抖动延时结束);输出变量包括EN-SCAN(扫描行转移)、EN-CODED(键盘编码启动)、START-TIMER(开启去抖动延时)。从图3中知道,状态S0→S1→S2为按键扫描状态键,状态S3→S4→S5为去抖延时状态链,状态S6为按键保持期。当按键被按下时,进入启动(S3)去抖延时状态链;去抖延时结束后(S5),若按键没有按下则恢复扫描状态键(S0);若按键确认被按下则进入保持期(S6),并输出按键编码,维持至按键松开。

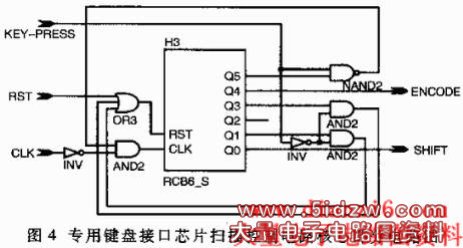

根据状态图3和上述的状态转移描述,进行键盘扫描控制电路的设计,结果如图4所示。其中H3是6位循环移位寄存器,由时钟CLK触发实时状态移位。移位寄存器的输出Q0~Q5分别代表键盘扫描控制电路的状态S0~S6,当然它们并非一一对应,但实现的功能相同。值得一提的是,如果专用键盘芯片KB-CORE的外部时钟CLK来自单片机的ALE信号(如图1所示),当单片机时钟为6MHz时,则专用键盘芯片KB-CORE的外接时钟为1MHz的方波信号,信号周期为1μs。如果将该时钟信号经过一个分频器,使其输出的信号周期约为Tclk=1μs×2 12≈4ms,然后再作为H3的时钟信号。这意味着键盘扫描控制电路约4ms扫描一行按键。如果H3中的Q2态没有被使用,则可以实现约8ms的去抖动延时。通过这样的设计,可以免除延时计数器,简化电路。

4 专用键盘接口芯片的实现

根据实时数据校正系统的设计要求,使用了34上自定义I/O引脚和PC44封装的CPLD来实现专用键盘接口芯片KB-CORE。芯片型号的选择依据综合所需要的宏单元(Macrocells)个数决定。如果借助硬件描述语言VHDL[5]对上述设计进行描述,综合结果需要约140个宏单元;如果改用原理图输入方式,则只需约60个宏单元。因此选用XC9572芯片可以满足上述专用键盘接口芯片KB-CORE的要求。实际使用如图1和图2所示。操作结果表明键盘接口芯片性能稳定。

,专用键盘接口芯片的一种CPLD实现方案