奔腾(Pentium)微处理器介绍

提高微处理器性能有三个途径:

提高芯片内部时钟频率使操作速度加快,这将受到微电子工艺及芯片功耗的限制。

增加数据总线宽度,提高数据路径的流量,这将要求芯片集成度提高、封装引脚增多。

微体系结构中采用新技术,使更多的指令在同一时刻并行执行(提高指令执行并行性ILP),这是最重要的一点,这将要求芯片有更高的集成度以及新的设计思想。

提高处理器指令执行并行性(ILP)有两种方法:采用超级流水线(Super-pipeline): 将指令的执行分解成小的步骤(级), 不同指令中不同步骤可并行操作。级数分的多,并行执行的指令也多。超级流水线指的是多级数的流水线(如8级以上)。采用超标量(Super-Scalar): 片内设置多重功能相同的部件,为指令并行执行提供硬件基础。第一代奔腾微处理器采用0.8微米工艺,集成度310万晶体管,工作频率66MHz,指令与486兼容,性能比486大大提高,是Inter芯片技术发展中的里程碑。

奔腾微处理器结构特点

哈佛结构,有分开的指令Cache与数据Cache,各8KB容量。

奔腾微处理器结构特点

独立的两条整数执行流水线,U与V,在一时钟周期内可以发射两条整数指令去执行。

采用转移预测策略,减少转移指令带来的流水线效能的损失。

Pentium 微处理器结构框图

Pentium 流水线

流水线和指令执行顺序:奔腾为超标量结构,两条五级流水线(U、V),可同时发射两条配对指令。U可执行X86任何指令,V执行“简单”指令。

预取指令级PF:从片内I-Cache取指令,有两个预取缓冲器,与分支目标缓冲器BTB协作,一个预取缓冲按顺序取指,另一个按转移指令目标预取,分支预测有结果后不管执行哪个指令流,均已预取好了。

流水线和指令执行顺序:

指令译码级D1:两个并行的指令译码器,依“指令配对法则”决定发射一条指令还是二条指令。

译码级D2:进行操作数地址计算,有专门地址生成部件。

执行级EX:做AUL及访问数据Cache的操作,复杂指令执行高效微码操作,比486快。

操作结果回写级WB:回写操作结果,修改状态,完成执行。

指令配对法则:两条流水线可以同时执行两条指令,但指令要满足一定配对规则。

两条指令必须是“简单”指令,硬线逻辑而不是微码实现,单周期执行, “简单”指令有规定。指令要在 I-Cache中。

成对指令无寄存器数据相关:

如 MOV eax,8 与 MOV eax,ebx 为输出相关;

MOV eax,8 与 MOV ebx,eax为指令流相关。指令中不能同时包含偏移量与立即数,等等。

转移(分支)预测:流水线执行过程中,条件转移指令的条件形成前,下条是执行转移目标指令还是顺序执行是个问题。

转移(分支)预测:设两个预测缓冲器,一个按顺序预取,一个按转移目标预取,不管转移与否,取指工作均准备好。设一个“分支目标缓冲器”(BTB),有256项。记录过去已执行过的转移指令的目标地址,还有2位标记,记录历史转移情况。

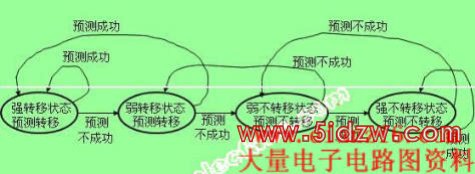

2位历史记录标记表示4种情况:“强转移”、“弱转移”、“弱不转移”、“强不转移”

转移(分支)预测:

动态预测中历史状态位的状态转换图

,奔腾(Pentium)微处理器介绍