标签:fpga是什么,fpga教程,fpga培训,http://www.5idzw.com

用Verilog HDL实现I2C总线功能,http://www.5idzw.com

字节发送模块的仿真测试结果如图1所示。

根据I2C总线标准,利用Verilog HDL很容易实现字节接收模块、开始条件模块、停止条件模块这三个模块。图2是数据发送过程的仿真测试结果。从器件的7位地址为101011,向从器件发送的数据为00010111。aensclo和aensdao分别是sclo/scli和sdao/sdai的切换信号。

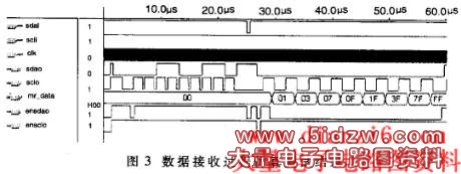

图3是数据接收过程的仿真测试结果。从器件的7位地址为0011001,从器件发送的数据为11111111。ensclo和ensdao分别是sclo/scli和sdao/sdai的切换信号。

将图2和图3所模拟的I2C总线时序与I2C总线协议中相关要求进行比较,满足I2C总线的时序要求。

对各个模块进行多层次处理,形成I2C总线模块。

以该I2C总线模块为基础,编写FPGA与AT24C01A(ATMEL公司生产的E2PROM)的通讯程序。然后把相关程序下载到EPF10Kl0LC84-3中,与AT24C01A进行实际通讯实验,效果良好。

,用Verilog HDL实现I2C总线功能