��������ʵ��

����Ƶ����幹˼������ѡ����ɺ�����еĹ����ǽ�����������ļ������ļ���Ҫ������������Ƶ�·�������ܡ�����ʹ�õ��ǣأɣ̣ɣΣع�˾�ṩ�Ŀ������ߣƣϣգΣģ��ԣɣϣ� ������������Ʋ���Ӳ���������ԣ֣ȣģ�����ƣ��䲿�ֳ������£�

��������� ������ ���

����� (

�����: ��� �ӣԣ� �̣ϣǣɣ�;

�����_����: ����� �����_������_���������(���� ��������� ��);��

�����_��: ����� �����_������_���������(���� ��������� ��));

���� ������;

���������������� ������_����� ��� ������ ���

����������� �������

�����( ������: ��� �����_������;

������ : ��� �����_������;

����: ��� �����_������;

���룰: ����� �����_������;

���룹�� : ����� �����_������;

���룱����: ����� �����_������;

���룲����: ����� �����_������;

���룲�� : ����� �����_������;

������: ����� �����_������;

�������: ����� �����_������);

���� �����������;

������

������ ��������� ��

�������� : ������� ����� ����� (

�� ���� �����,

�� ���� ����);

������: ������� ����� �����( ������ ���� ����,

���� ���� ������_��,

������ ���� ������,

���룰 ���� ���룰,

���룹�� ���� �����,

���룱���� ���� �����,

���룲���� ���� �����,

���룲�� ���� ���룲��,

������ ���� ������,

������� ���� �������

);

������_���룰: ������ ����� ����� ( �� ���� ���룰,

�������_������;

);

�����⣼������_������;

��������(���룲��);

������

��� ���룲���������� ���� ���룲�����䣱�� ������

����_���� �������� ��������

����_���������� ��������

�����_������������������_������

�����_������������������_������

��

��

�����_��������������������_������

�����_����������������_��������

�����_����������������_��������

��

��

�����_������������������_��������

���� ��棻

���� ��������

���� ������_����裻

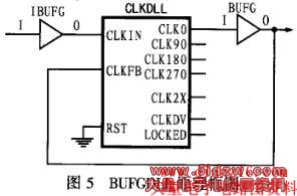

������FPGA�ĸ�Ƶʱ�ӵķ�Ƶ�ͷ������