1.引言

USB2.0摄像头微处理器支持高速USB2.0接口,内嵌强劲的图像后处理单元,JPEG高速编译码器,支持高达200万像素的CMOS传感器接口和CCD传感器接口,处理器设计的产品可以实现独特的运动监测功能与脸部追踪功能,这不仅大大加强了显示效果,提高了画面的品质,更拓展了PC摄像头的应用领域,如增强的实时视频聊天功能和门禁监测系统。

主要功能:USB2.0高速传输并兼容USB1.1;高速图像后处理单元;JPEG高速编译码器;VGA下30帧/秒高速传输;CMOS/CCD接口;内置8比特微控制器。

不仪具备以上的先进特性,还拥有以下多种可扩展性:多个GPIO接口为增加连拍、LED指示灯、快捷键等功能提供了无限可能;USB2.0兼容USB1.1,为摄像头的广泛的使用增加了保障;支持多种操作系统,如64-bit Window,Windows XP,Linux,Mac,VxWorks,WinCE等等。以下就是对USB2.0摄像头微处理器的硬件设计方法及外围电路分布的介绍。

2.系统硬件设计

2.1 振荡器

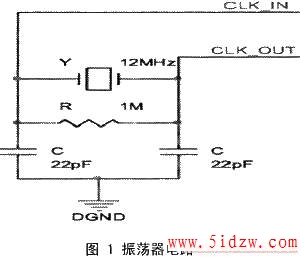

USB2.0摄像头微处理器的钟频是12MHz,外部时钟频率稳定性必须小于±50ppm。图1是振荡器电路的设计参考图。

2.2 复位

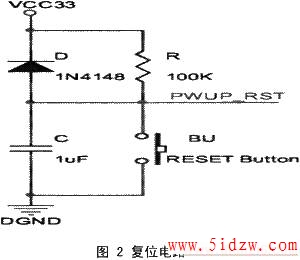

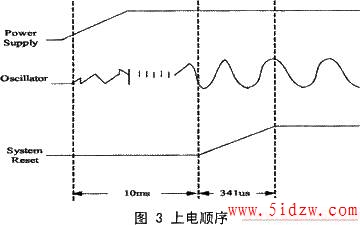

上电后,复位信号必须在低设置处停上最少10ms,才能使来自振荡器的信号稳定。芯片集将在341μs后进入稳定状态。

图2展示了复位电路。二极管(D)在电力关闭时用于加快电容器(C)放电的速度。如果PCB空间不足,可选择将D去除。图3为上电顺序。

2.3 电源和地

2.3.1 电源和地的类型

电源供应是由数字部分和模拟部分构成。

2.3.2 电源电路

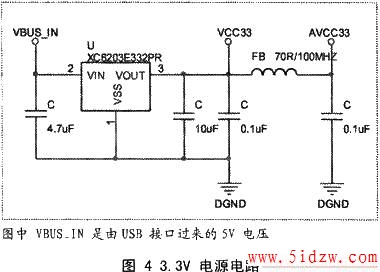

该电路使用的是单一电源供应模式。由外接电源供应3.3V的I/O电到芯片,再由其内置的PR(电源调节器)输出1.8V从DVDD引脚供应到USB-VDDL。内置PR电路需要将最少为10uF的电容放在与DVDD引脚最近的位置上。这些调节器必须能够做到在进入待机模式时自动转为低功耗状况。图4为3.3V电源电路。

3、外围电路分布

USB2.0摄像头微处理器的外围接口分布主要有:USB2.0接口;EEPROM接口;传感器接口;其它功能PIN接口和USB2.0 PCB排版。

3.1 USB2.0接口

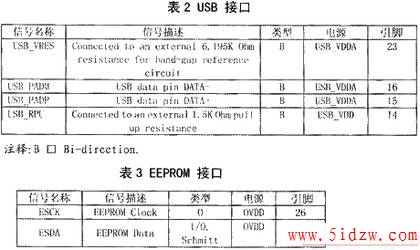

USB2.0接口如表2所示。

USB_VRES是USB接口的电压参考值。USB_VRES的下拉电阻应该更为准确(推荐值6.2K±1%Ohm)。

3.2 EEPROM接口

EEPROM接口如表3所示。

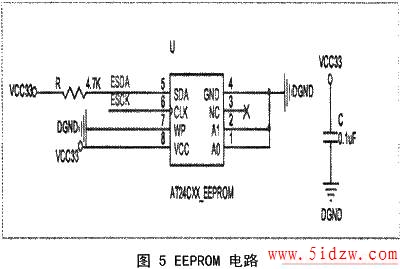

如需要添加新的VID和PID或传感器配置,则需用一个2-线串行EEPROM。图5是EEPROM的应用电路。

ESCK引脚是用来选择EEPROM大小的。当EEPROM大于16k bit时则需要一个上拉电阻。当EEPROM小于或等于16k bit时则将ESCK下拉。当要支持一颗新的CMOS传感器芯片时,则需外挂一颗64k bit的EEPROM。

EEPROM可帮助更改PID,但在没有EEPROM时,ESCK引脚可用来做PID的选择。

3.3 传感器接口

传感器接口有10根(10-bit)数据线。当传感器只有8根(8-bit)数据线被采用时,低两位数据线(CS_D1,CS_D0)应接成LOW的级别。在CS_CLK和CS_PCLK pin脚处接一个电阻(推荐220hm)并将它们与DSP放置的越近越好以用来减少反射的信号。

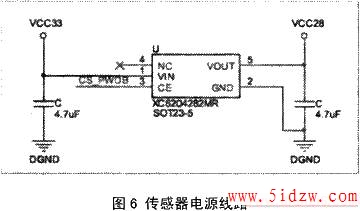

CS_SCK和CS_SDA都被用做为opendrain,从内部上拉。CS_PWDB控制传感器的电源。当视频打开时,CS_PWDB从低设定转变为高设定以开启传感器的电源。当视频关闭后,CS_PWDB的运作则反转过来以关闭传感器的电源。在待机模式下,由于USB待机电流限制是500uA,所以CS_PWDB也可输出低级别的设定。

如果PIXCLK没有给芯片反馈,传感器也可以通过设置EEPROM来运行。

3.4 其它功能引脚

TEST引脚需要用一个47KOhm的电阻将其连接到地。GPIO_FLIP和PRIVACY在正常情况下应接成HIGH。如果GPIO_FLIP是LOW,图象会旋转180度。如果PRIVACY是LOW,图象会转黑。如果需要SNAPB功能,可接一个4.7KObm的电阻到I/OPower并接一个按钮到地,按下这个按钮即可拍静态图。GPIO_PWM是用来输出一个PWM信号的。

3.5 USB2.0 PCB排版指南

USB DP和DM的传送行程由高速(F/S)USB2.0的设计指导方针来确定。

USB DP和DM的差分线阻抗是90ohm±15%。

为将ESD免疫性最大化,工业设计需使USB连接处暴露的越少越好。

USB DP/DM的连线要宽于22 mil(1mil=25.4μm)并有7 mil间距。按要求在DP/DM连线下需要有一条持续的地线,同时DP/DMPCB的后面的地线是不能分开的,也不能有通孔。

需确保不相关的信号连线、电源及元件远离DP/DM的连线。一个通用的标准是保持最少35mils的距离。

将大的电容器保持在USB_5V电源连接口处。

退耦电容器需放置在最接近芯片处。

如有需要可将一块铁氧体放置在USB_5V处用来扩大ESD免疫性。如不需要可在板上放置0Ohm的阻抗。铁氧体必需是低DCR(<100mOhms)。如果是用mini-B型接口,则需将铁氧体放置在与芯片不同的板层。

,USB2.0摄像头微处理器硬件设计