GAL(Generic Array Logic)是一种电擦除可重复编程的可编程逻辑器件,具有灵活的可编程输出结构 ,使得为数不多的几种GAL器件几乎能够代替所有PAL器件和数百种中小规模标准器件。而且,GAL器件采 用先进的EECMOS工艺,可以在几秒钟内完成对芯片的擦除和写入,并允许反复改写,为研制开发新的逻辑 系统提供方便,因此,GAL器件得到了广泛的应用。

GAL可分为普通型GAL和新一代GAL两类,普通型GAL器件与PAL器件有相同的阵列结构,均采用与阵列可 编程、或阵列固定的结构。普通型GAL器件有GAL16V8,CAL16V8A,GAL16V8B及GAL20V8,GAL20V8A, GAL20V8B;新一代GAL的与阵列和或阵列都可编程,如LATTICE公司的GAL39V18等。下面以GAL16V8为例介绍CAT器件的基本组成原理。

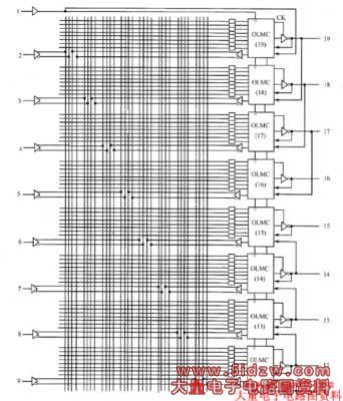

图1所示为GAL16V8的逻辑图,它由输人缓冲器(左边8个缓冲器)、输出三态缓冲器(右边8个缓冲器) 、与阵列、输出反馈/输入缓冲器(中间8个缓冲器)、输出逻辑宏单元0LMC(其中包含或门阵列),以及 时钟和输出选通信号缓冲器组成。GAL器件的可编程与阵列和PAL器件相同,由8×8个与门构成;每个与门 的输入端既可以接收8个固定的输人信号(2~9引脚),也可以接收将输出端(12~19引脚)配置成输人 模式的8个信号。囚此,GAL16V8最多有16个输人信号,8个输出信号。GAL器件与PAL器件的主要区别在于 它的每个输出端都集成有一个输出逻辑宏单元。下面重点分析GAL器件的输出逻辑宏单元。

图1 GALlGY8逻辑图

图2所示为GAL器件输出逻辑宏单元OLMC的结构图。由图可知,0LMC是由一个8输人或门、一个异或门、一个D触发器和4个数据选择器组成。8输人或门接收来自可编程与阵列的7~8个 与门的输出信号,完成乘积项的或运算。异或门用来控制输出极性。当XOR(屁)=0时,异或门输出极性 不变;当X0R(n)=1时,异或门输出极性与原来相反。D触发器作为状态存储器,使GAL器件能够适应于 时序逻辑电路。4个多路数据选择器是0LMC的关键器件,它们分别是乘积项数据选择器(PTMUX)、输出三 态控制数据选择器(TSMUX)、输出控制数据选择器(0MUX)及反馈控制数据选择器(FMUX)。

图2 GAL的输出逻辑宏单元

1.乘积项数据选择器PTMUX

乘积项多路选择器PTMUX用于控制来自与阵列的第一个乘积项,完成二选一功能。若信号ACo・AC1(n) =1,则第一乘积项作为8输入或门的一个输人项;若为0,则该多路选择器选择地信号送或门输人端,这 时或门只能接收7个来自与阵列的乘积项。如果输出三态门不用第一个乘积项控制,多路选择器将选择乘 积项送或门输人端,这样或门可以接收8个与阵列输出的乘积项。

2.输出控制数据选择器0MUX

输出控制多路选择器OMUX也是一个二选一多路选择器,它在信号ACo+AC1(n)的控制下,分别选择异或 门输出端(称为组合型输出)及D触发器输出端(称为寄存型输出)送输出三态门,以便适用于组合电路 和时序电路。若ACo+AC1(n)为0,则异或门的输出送到输出缓冲器,输出是组合的;若为1,则D触发器 的输出Q值送到输出缓冲器,输出是寄存的。

3.输出三态控制多路选择器TSMUX

输出三态控制多路选择器TSMUX是一个四选一多路选择器,其受信号ACo,AC1(几)控制,若ACoAC1(n )为00,则取电源Vcc为三态控制信号,输出缓冲器被选通;若为01,则地电平为三态控制信号,输出缓 冲器呈高阻态;若为10,则OF,三态控制信号;若为11,则取第一乘积项为三态控制信号,使输出三态门 受第一乘积项控制。

4.反馈控制数据选择器FMUX

反馈控制多路选择器FMUX也是一个四选一多路选择器,用于选择不同信号反馈给与阵列作为输入信号, 它受ACo・AC1(n)・AC1(m)控制,使反馈信号可为地电平,也可为本级D触发器的Q端或是本级输出三 态门的输出,当ACo・AC1(n)・AC1(m)为01时,反馈信号来自邻级三态门的输出,由于邻级(m)电路 的ACo・AC1(m)=01,其三态门处于断开状态,故此时是把邻级的输出端作为输人端用,本级(n)为其 提供通向与阵列的通路。

图2中异或门用于控制输出信号的极性。当X0R(n)=1时,异或门起反向器作用,再经过输出门的反向 后,使输出为高电平有效。当X0R(n)=0时,异或门输出与或门输出同相,经输出门的反向后,使输出 为低电平有效。ACd,AC1(n),X0R(n),AC1(m)及SYN都是0LMC的控制信号,它们是结构控制字中的 可编程位,由编译器按照用户输人的方程式经编译而成,其中X0R(n)和AC1(n)是每路输出各有一位, n为对应的0LMC的输出引脚号,而阴则代表相邻的一位,即m为而+1或n-1,视屁的位置而定。ACo只有一 个,为各路所共有。SYN也只有一个,它决定CAL是皆为组合型输出,还是寄存型输出,并决定时钟输入Ck 和外部提供的三态门控制线0E的用法。若SYN=1,则所有输出都没有工作在寄存器输出方式,1脚(Ck)和 11脚(0E)都可作为一般的输人来用。若SYN=0,则至少有一个工作在寄存器输出方式,1脚(Ck)和11 脚(OF,)就不能当作一般的输入来用,而必须分别作为时钟输人端和输出三态门的使能端。

综上所述,可见GAL有以下几种工作方式。

①纯输人方式:1脚和I I脚为数据输人端,三态门不通(呈高阻抗)。

②纯组合输出:1脚和Ii脚为数据输人端,所有输出是组合型的,三态门总是选通的。

③带反馈的组合输出:1脚和11脚为数据输人端,所有输出是组合型的,但三态门由第一乘积项选通。

④时序方式:1脚=Ck,11脚=0E,至少有一个宏单元的输出是寄存型的。

欢迎转载,信息来源www.5idzw.com(www.5idzw.com)

,GAL器件的基本结构