图3 九进制计数器

由图可知,74LSl61从0000状态开始计数,当输人第9个CP脉冲(上升沿)时,输出Q3Q2Q1Q0=1001,此 时CR=Q3Q0=0,反馈给CR端一个清零信号,立即使Q3Q2Q1Q0返回0000状态,接着CR端的清零信号也随之消 失,74LS161重新从0000状态开始新的计数周期。需要说明的是,此电路一进人1001状态后,立即叉被置 成0000状态,即1001状态仅在极短的瞬间出现,因此,在主循环状态图中用虚线表示。这样就跳过了1001 ~1111共7个状态,获得了九进制计数器。同理,如果将74LS16l换成74LS160,也可构成九进制加法计数 器。

4,数字钟

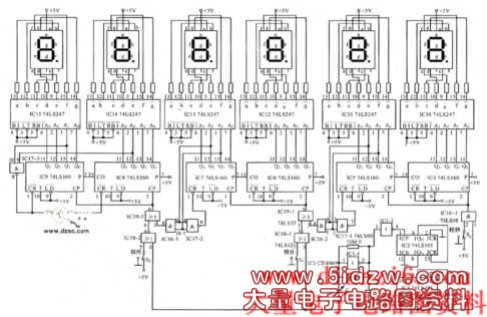

数字钟由石英晶体振荡器、分频器、计数器、译码器、显示器和校时电路组成,石英晶体振荡器产生的 信号经过分频器变为秒脉冲,秒脉冲送人计数器计数,计数结果通过“时”、“分”、“秒”译码器显示 时间,电路如图4所示。

①振荡器:由CC4069非门IC1-1,IC1-2,f0=32768Hz的石英晶体振荡器、电阻和电容组成。由ICl-2 的4脚输出的频率为32768Hz的方波。

②分频器:由两个74LS393 IC2,IC3组成,74LS393是双4位二进制计数器,32768Hz的方波与IC2的I脚相 连,输人时钟脉冲,两个74LS393组成分频器,32768=215,因此,由9脚输出秒脉冲。

③计数器:由6个74LS160 IC4,IC5,IC6,IC7,IC8,IC9和相应的门电路四2输人与门74LS08、四2输人 与非门74LS00等,分别组成60进制“秒”计数器电路、60进制“分”计数器电路和24进制“时”计数器电 路。

④译码和显示电路:由6个74LS247 IC10,IC11,IC12,IC13,IC14,IC15,IC16和6个数码管组成。

⑤时间校准电路:其作用是当计时器刚接通电源或走时出现误差时,实现对“时”、“分”、“秒”的 校准,由四2输人与门74LS08、四2输入或门74LS32、四2输人或非门74LS02等组成。

图4 数字钟电路

欢迎转载,信息来源www.5idzw.com(www.5idzw.com)

,中规模时逻辑集成计数器