1 引言

FPGA的出现大大缩短了集成电路设计的周期,使产品上市的时间大大缩短,并减少了设计成本。FPGA的应用越来越广泛,并且其市场份额也越来越大。但是逐渐扩大的芯片规模和更加复杂的芯片结构,给测试带来了越来越大的困难,测试成本大大增加,如何降低测试成本是很多商家和研究者共同面对的一个问题。有关FPGA测试的研究有很多。

FPGA主要由可编程逻辑资源,可编程连线资源,可编程输入输出资源组成。其中连线资源占芯片面积的60%以上,并且随着器件规模增大,连线也越来越复杂,其出现故障的可能性很大,所以连线资源测试在FPGA测试中扮演了一个很重要的角色。芯片测试包括故障检测、故障诊断和故障冗余。故障检测只检测芯片中有没有故障,如果芯片中有故障就把此芯片扔掉;故障诊断不仅要检测芯片中是否有故障,还要确定故障的位置和类型;而故障冗余是指,对于有故障的芯片采取一定的方法使得芯片可以继续使用,而不至于浪费。可以看到,故障检测是故障诊断的基础,而故障冗余又以故障诊断为前提,在本文的设计中,故障检测及故障诊断都可以支持,只要设计好需要的测试配置就可以了。

对于连线资源测试,出现了很多种方法,大致分为三类:(1)非内建自测试方法(Non―BIST),利用专有的测试仪器对芯片进行配置并加测试向量对芯片进行测试;(2)利用芯片内部可编程逻辑资源对连线资源进行测试,这是内建自测试方法(BIST),在芯片内部通过配置可编程逻辑资源自动产生测试向量,并且对测试结果进行判断。以上两种方法都是利用FPGA的可编程特性对芯片进行测试的;(3)利用可测试设计方便芯片进行测试,通过一定的硬件消耗,在芯片内部加上一定的辅助电路,使得测试比较方便、快速。本文提出的方法属于第三类方法。

与ASIC测试不同,FPGA测试需要将测试需要的配置下载到芯片中,然后加测试向量对芯片进行测试,其测试时间主要由编程下载的时间来决定,所以编程下载时间决定了测试的成本,很多研究者通过减少测试配置数目来减少测试时间,从而降低测试成本。

本文的出发点不是通过减少测试配置数目来减少测试时问,而是从另外一个角度对测试开关盒连线资源时间的减少进行了研究。通过一定的硬件消耗大大减少了编程下载的时间,降低了测试成本。

2 基于SRAM的FPGA结构简介

FPGA通常有三个基本的组成部分,即可编程逻辑单元((Sonfigurable Logic Block,以下简称CLB)、可编程输入输出单元(Input and Output Block,以下简称IOB)及可编程连线资源。通常CLB包含组合逻辑部分和时序逻辑部分,组合逻辑一般包括查询表(Look―up Table)和相关的多路选择器(Multiplexer)。而时序逻辑部分包含触发器(DFF)和一些相关的多路选择器。IOB则提供了FPGA内部和外部的一个接口,连线资源则提供CLB与IOB之间以及各CLB之间的通讯。

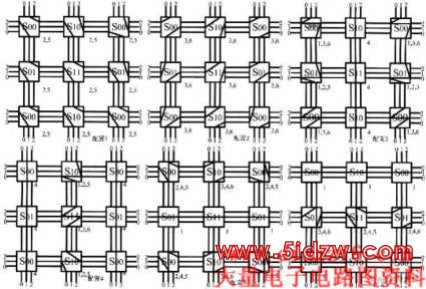

FPGA芯片的基本结构如图1其原因所示,现在的FPGA芯片结构越来越复杂,但都包含这些基本的组成部分。开关盒(Switch Box,以下简称SB)将水平和竖直连线资源进行切换。连接盒(Connection Box,以下简称CB)连接CLB的输入输出到连线资源中。在FPGA芯片中,由于连线资源比较复杂,所以测试花费时间会很长。其中把开关盒抽出来可以构造开关盒资源图,其中包括开关盒内部的可编程开关以及开关盒之间的连接线段,如图2(a)所示。

FPGA开关盒资源模型包括m×m个SB以及相邻的SB之间连接开关盒的k条连接线段,其中SB内部的连接关系如图2(b)所示。其中粗线代表一个NMOS管作为传输管,用来控制线段的连接,传输管的开和闭由编程信息来控制,编程信息存储在SRAM单元中。SB内部有很多传输管,其中两条线段之间有传输管相连的,称为可连接线段,没有传输管的,称为不可连接线段。图2(c)是抽象的开关盒连接关系,其中四个方向分别为T,B,L,R,黑点表示此方向的连接线段的集合,每条连接线段可以另外三条连接线段连接,这三条连接线段分别位于其他三个方向,其中的数字表示传输管的编号。比如3,表示左边的连接线段连接上边的连接线段。

在FPGA连线资源中,主要包含连接线段,传输管和CB中的连线资源。连接盒一般和逻辑资源放在一起进行测试,本文着重于开关盒连线资源的测试。

3 测试所需要的配置

3.1 测试采用的故障模型

1)线段开路故障,线段在制造过程中中间断开,不能正常传输信号,输出端的状态固定;

2)线段的固定O故障,不管输入信号是0还是l,线段总固定在0状态;

3)线段的固定l故障,不管输入信号是0还是1,线段总固定在1状态;

4)传输管的固定0故障,也就是常开故障,SRAM编程信息不能改变此开关的状态;

5)传输管的固定l故障,也就是常闭故障,SRAM编程信息不能改变此开关的状态;

6)线段的桥接故障,两条线段之间短路,当分别在桥接的两条金属线上加相反的信号时,因为桥接两线的输出信号是相同的。

3.2 测试所需配置

在测试之前,需要将配置信息下载到FPGA芯片中,然后施加测试矢量进行测试。本文以[3]中的配置为例说明此可测性设计,在此采用Wilton开关盒结构,配置原理与[3]一样。测试配置如图3所示。

上述的7种配置中同一个SB内编号相同的开关的状态都是一样的。配置中SB旁边的数字表示SB内需要闭合的传输管的编号。图中SB的编号Smn,其中:S00:处于奇行奇列的SB;S01:处于偶行奇列的SB;S10:处于奇行偶列的SB;S11:处于偶行偶列的SB。编号相同的SB在同一个测试配置中状态是完全一样的。如果对故障进行诊断,需要配置1到配置6。

1)配置l和配置2能够诊断任何单个线段开路故障、线段固定故障和线段桥接故障;

2)配置l、2、3、4、5和配置6能够诊断任何编号为3、6的单个传输管固定O故障;

3)配置1、2、3、4、5和配置6能够诊断任何编号为2、5的单个传输管固定0故障;

4)配置3、4、5和配置6能够诊断任何编号为4、1的单个传输管固定0故障;

5)配置l(或配置2)、配置3和配置4能够诊断任何编号为l的单个传输管固定1故障;

6)配置1(或配置2)、配置3和配置4能够诊断任何编号为4的单个传输管固定1故障;

7)配置3、4、5和配置6能够诊断编号为2、3、5、6的单个传输管固定1故障。

如果仅仅是进行故障检测,配置1、2和配置7就够了。

4 移位寄存器链测试方法

由于FPGA规模越来越大,编程SRAM单元数量巨大,下载测试配置的时间就非常大。在测试中,需将配置下载到芯片中,然后加测试矢量对连线资源进行测试,但是在下载的过程中,也同时将逻辑资源的编程数据下载到了芯片中,这种下载对测试连线资源是没有用的,所以这部分时间对连线资源测试来说是多余的。

从图2的开关盒连接关系和图3中的测试配置可以看出,在一个开关盒内部编号相同的开关状态是一样的,所以在这种情况下就可以在开关盒内部增加6个触发器,每个触发器的输出端连接到相同编号的所有传输管上,并且将所有的触发器连接成多条移位寄存器链,这样在配置的时候就可以将事先设计好的配置数据通过移位寄存器链下载相对应的开关盒内SRAM单元中,每个触发器可以并行配置与其相连的SRAM单元,时间又可以节省很多。如图4所示。各信号意义如下: