����ժҪ������Ŀ���Ǹ��ݺ��������Ƶ���Ҫ�����һ�ָ߿ɿ�����������Ƶ���Ʒ������ڷ����˵�����ЧӦ�ĺ��ܽ��˸߿ɿ�����Ƽ����Ļ����ϣ��� oregano systems��˾�ṩ�� mc8051IP���˽������ġ��ĺ�� IP���������Ҫ�������ȶ�������ʵ����˵������Ʒ���������ʵ�ּ��߱�ʵ�ü�ֵ��

��������

���������ҹ�������ҵ�ķ�չ�����ܶȼ��ɵ�·�����ں������������б�����ʹ�ã�Ȼ�������������ɶȵ���ߺ�����ѹ�Ľ��ͣ��ռ���价���Ե���ϵͳ��Ӱ��Խ��Խ�ࡣ�ռ���价���Ե���ϵͳ��������Ҫ���ǵ�����ЧӦ(Single Event Effect) �����ǻ�ʹ����ʧЧ���߹���״̬�����ı䣬Ӱ������豸�Ŀɿ����� 5�����ڱ������ڵ�λ�е��Ĵ������칤�������йؼ���λ��ʹ���� 8051�����������ĸ��ݺ��������Ƶ�Ҫ���һ��8051IP���˽������ģ�����Ӧ�����豸����Ҫ��

����1 mc8051IP�˽���

����IP��Intellectual Property)ԭ��ָ֪ʶ��Ȩ���� IC�����������ָԤ�����ʵ��ij�ֹ��ܵ�ģ�顣IP��(IPģ��)����ָ���ij�ֹ��ܵ������·ģ�飬Ҳ��֮Ϊ���ⲿ����

�������� IP���ṩ��ʽͨ���� IP�˷�ΪӲ IP(Ӳ�� Hard Core)���� IP(���� Soft Core)�� IP(�̺� Firm Core )��

����Ӳ�������ij���ض����յ�һ��������ͼ����·���ֲ��ߺ�����ȷ���ģ��Ѿ�����Ʒ��·����֤��Ӳ�˵��ŵ������ĸ��ٶȺͰ�ȫ�ԣ������������ض��Ĺ��գ�����ȱ������ԡ�

������������Ӳ����������(Verilog HDL�� VHDL)����ʽ�������ܿ����Ϊ�����Dz����漰��ʲô��·�͵�·Ԫ��ʵ����Щ��Ϊ�����˾��е��ص��ǿ��Ը����û���Ҫ���Ľ����Ķ��ơ�

�����̺���һ�ֽ������˺�Ӳ��֮��� IP�ˣ�ͨ���� RTL����Ͷ�Ӧ���幤�������Ļ����ʽ�ṩ���̺���������ۺϵĹ��ܿ飬�нϴ�������ȣ�ͨ������������ʽ�ύ�ͻ���

����mc8051IPcore�� Oreganosystems��˾�ṩ��һ��Ӧ�ù㷺�Ŀ�Դ 8051IP���ˡ�

���������������㵥Ԫ����ʱ�� /�����������ڣ��ڲ� ram���ⲿ ram�� rom��ɡ�mc8051_aluΪ���㵥Ԫ���ɼӷ������˷������������Ȼ������㵥Ԫ��ɡ�mc8051_controlΪ mc8051�Ŀ���ͨ·������������Ĵ��������뵥Ԫ����·ѡ�������жϼ�ָ��״̬���Ȼ������ܡ�2�������ӿɿ�����Ƽ���

�����ɿ�����ƵĻ���ԭ�������࣬������Ϣ���࣬ʱ������ȡ�Ŀǰ��������ЧӦ����Ƽ�����Ӧ�����ļ�������ģ����(Triple Modular Redundance ��TMR),���������Error Detection And Correction ,EDAC�� 1���������Ŀ��������

����2��������Ҫ����ǰ2�ֿɿ�����Ʒ�����

����2.1 ��ģ���ࣨTMR������

������ģ������ָ��Ŀ�겿���������ͬ������Ŀ�겿����ʵ��һ��Ŀ�겿���Ĺ��ܣ�����Ŀ�겿�����ս�ͨ��һ���о������ж�Ŀ�겿������ȷ״̬�������õ�����ͬһ�鲿��ͬʱ���ִ�����ʽ�С��ԭ����ʵ�ֿɿ��Ե���ߡ�

����TMR�����ڸ���IP��Ƶĸ��Σ��ȿ�����ϵͳ���������࣬Ҳ�����Ǿֲ����ࡣ

����2.2 ���������EDAC��

����2.2.1 EDAC����

����EDAC���������������豸����SEU����Ĵ洢Ϊ��ת����EDAC�Ļ����ṹ����3�����֣�����ģ�飬����ģ�飬�洢ģ�顣����EDAC����ģ�齫��Ҫ���������ݽ�������㷨�ı��룬����У���룬�����������һͬ����洢ģ�顣������Ҫ������ʱ��EDAC����ģ�齫��������ӦУ������н��봦�����ó���ȷ�ṹ����������������õı��뷽ʽ���Ը�����Ҫѡ���纺���룬�����Ȩ�룬��ԭӢ����ȵȡ�

����2.2.2 ���������

������������չ������Ϊ��˵��������������ԭ���� ��չ�����루Extended Hamming Code���ڴ洢ϵͳ�ľ�������еõ��˹㷺Ӧ�á�������С�����4����������λ�� k��У��λ�� r������֮��Ĺ�ϵ������ 2r-1 �� k+r���������λ k����һ����У��λ rҲֻ��Ҫ����1λ�������������൱�ߵı���Ч�ʡ� 8λ���ݾ���4λ���������ݽṹ���£�

����C= [D7D6D5D4D3D2D1D0C3C2C1C0]���� D7��D0������λ��C3��C0��У��λ��

����C3= D7 ��D6 �� D5 �� D4 �� C2= D7 ��D3 �� D2 �� D1�� C1= D6 ��D5 �� D3 �� D2 �� D0 �� C0= D6 ��D4 �� D3 �� D1�� D0

��������ʱ�����洢���ݵİ������� S: S3= C3 ��CB3��S2= C2 ��CB2 ��S1= C1��CB1��S0= C0 ��CB0 ���� CB0��CB1,CB2,CB3Ϊ 8λ�����ڽ���ʱ�̵�У��λ��������õİ������� S���ǾͿ����ж�����λ�Ƿ�������������λ�á�

����2.3 ���־��������ıȽ�

����TMR�� EDAC������Ӳ�����࣬���ڲ�ͬ�ֳ��Ĵ洢����������ռ�õ����������ʱ�俪���Dz�ͬ�ġ�TMR��ռ�õ�����������������2��Ŀ�������Լ��о�����������·����EDAC�����ӵ������������������ӵ�У��λ������������������������ 1���������Ϸ������ǿ��Եó����ۣ����ڱ����Ĵ������Ĵ������������С�Ĵ洢������TMR��ʵ�ּ�����������ٵ��е㡣�����ڴ������Ĵ洢������Ӧ������ EDAC�����о��������

����3�߿ɿ��� 8051���巽����Ƽ�ʵ��ͨ���� SEU�Ļ��������� mc8051�ṹ�������Եó��������ܵ����ӷ���Ĺؼ���λ��

����3������Ĵ�����Special Function Register ��SFR�����ڲ� ram���ⲿ ram�������ľ���������ģ��� mc8051IP�˽����˸ý���

����3.1����Ĵ�����SFR��

����mc8051IP�˵�����Ĵ���(SFR)���� control_mem�ļ���ʵ�֡���ģ��ʵ�� 8051���빦�ܡ�SFR�ֽڵ�ַ��Χ��80H-FFH�������� RAM�в�������ȫ�����ģ�21�� SFR��ɢ�ķֲ��������ֽ������128���ֽڵ�Ԫ�С���mc8051IP���в�û�ý���ЩSFR������ڲ� ram�У����Ƕ�Ӧ��ַ�ֱ�ʵ�ֵġ��� SFR�ļӹ̴����Dz����� TMR����������ʵ�ֲ������£�

�����ۺϺ�����ȡ����ͼ��

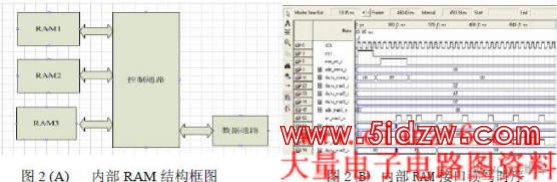

����3.2�ڲ� RAM

������ IP�˿�֧�� 128�ֽ��ڲ�RAM.�� 2.3�������������� TMR��ʽ���ڲ� RAM���д�����ѡ�� 3����ͬ�� 128�ֽڵ� RAM��Ϊ����Ĵ洢������ mc8051_ram_fsm�� mc8051_ram_dataflow����ģ��������ڲ� RAM������ͨ·������ǰ�����д���ȵĶ�д״̬���ƣ������������������ơ�����ͨ·�����������У�顣����ͨ·������ͨ·����ڲ� RAM�ӿ���������������ڲ� RAM�ӿڽṹ��ͼ����дʱ�����£�

����ͼ 2(B)�ɿ�����д����ʱ�����������ڶ������ڱ�д��RAM��������ʱ����ָ�����ĵ� 5�����ھ�У������ȷ���ݱ�������ұ���д��RAM���ڽ��빤��Ӧ��ʱ�轫�ⲿʱ�ӽ��� 6��Ƶ����� cpu��дʱ��

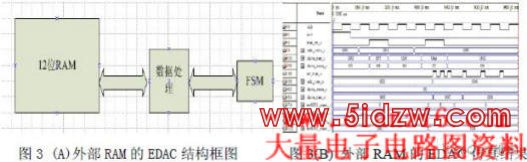

����3.3 �ⲿ RAM

�����ⲿ RAM������֧��64K��ͬ���� 2.3����������ѡȡ�ܾ� 1λ���� 2λ������չ��������� EDAC���������У����ݴ�����Ԫ������ݵı��룬���룬��ַ���漰����������ܡ���д״̬�� FSM����ⲿ RAM�Ķ�д״̬���ƣ�ͬ����Ϊ��� ram�� IP����ʱ�����ǽ� FSM���Ϊд���ȡ������� EDAC�ṹ��ͼ����дʱ�����£�

������Ҫָ����ʱ��ͼ����ʱ�ⲿʱ��Ϊ 10Mhz,���� altera��˾ alt_PLL������ 6��Ƶ����λ������ǰһ��дָ��δ��ִ�е�ԭ���� PLL��Ҫ 2�� 3��ʱ�����ڵĵ����ȶ�Ƶ������� EDACģ��Ķ�дʱ�����ڲ� RAM���ƣ�д����ʱ�� 2��ʱ�����ھ���������� 8λԭ�����Լ� 4λУ������һͬ��д�� RAM��������ʱ�������� 12λ���ݾ�������������ڵ� 5��ʱ��������� 8λ���ݲ���������� 12λ���ݻ�д�� RAM���Է�ֹ SEE�Ļ��ۡ���ʱ��ͼ��֪���������ȫ�������Ҫ��

���߿ɿ�������������о�