2.4 匹配相乘模块

匹配相乘模块主要完成的工作,是把距离脉冲压缩的数据经FFT后的结果与匹配函数对应相乘,再把相乘的结果送出。匹配相乘模块的核心是复数乘法器。复数乘法器是由4个普通乘法器和两个加法器组成。假设完成(a+bi)×(c+di)的操作,先分别计算a×c,a×d,b×c,b×d这4个实数与实数的乘法运算,再把减法运算a×c-b×d结果作为复数乘法器输出的实部,加法运算a×d+b×c的结果作为复数乘法器输出的虚部。

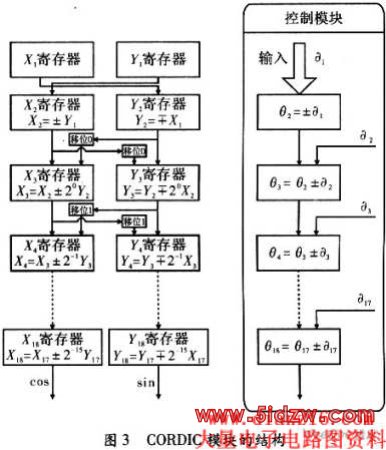

对数据的同步也是设计的重点。因为距离脉冲压缩经FFT后的数据与匹配函数的数据并不是同时进入匹配相乘模块。距离脉冲压缩经FFT后的数据较先进入,主要是因为匹配函数运算的CORDIC采用流水线结构,需要18个时钟周期来获取第一个计算结果而产生匹配函数数据的延迟。所以应该对匹配相乘模块对距离脉冲压缩经FFT后的数据进行缓冲。缓冲采用FIFO模块来实现。FIFO可以采用自带的IP core。

3 波形仿真与性能分析

验证方法采用比对的方法,即单个目标点的仿真数据分别进行理论方位脉冲压缩仿真和基于FPGA的方位脉冲压缩仿真,并将得到的仿真结果进行比对。仿真数据中一个距离单元的点数为16 384点。验证过程是首先在。Matlab软件环境下对单个点目标的一个距离单元进行方位脉冲压缩的仿真,即理论仿真,然后再在Modelsim环境下对该距离单元进行方位脉冲压缩的FPGA仿真,并将得到的结果与Matlab下得到的理论结果进行比较。其比较的波形,如图4所示。

选用Ahera公司芯片EP2S130F780C5进行测试。稳定工作时时钟频率可以达到150 MHz。

4 结束语

方位脉冲压缩系统是这个R-D算法在FPGA实现的关键。文中给出的方案通过实验验证能够达到设计的要求。实验表明,随着可编程器件规模、速度的不断提高,采用FPGA实现高速数字信号处理的算法具有可行性和优越性。

,基于FPGA雷达成像方位脉冲压缩系统的设计