标签:传感技术知识,传感器与检测技术,http://www.5idzw.com

高端路由器设计需要考虑的数据缓冲器问题,http://www.5idzw.com

异步设计中的时钟同步也是一个应该考虑的问题。在大多数路由器环境中,进入系统的传输线路与主系统时钟会在不同的时钟域中运行。设计师必须连接不同宽度的总线。路由器设计师面临的一个常见的挑战就是如何使用数据缓冲器使这些全异时钟同步,并复用16 位和 32 位或 32 位和 64 位之间的数据,以确保整个系统中数据的完整性。

设计师使用基于FPGA的方法调整他们的逻辑以实现上述目标。然而在一般情况下,该工作需要丰富的电路设计专业知识以及模拟和测试这些电路的时间。相比之下,许多高性能 FIFO 提供的嵌入式总线匹配能力可自动解决这个问题。这些器件可提供多总线宽度和端口可选的总线宽度匹配,有助于出口线路和入口线路之间的无缝连接。这些器件也具备独立的读写时钟,可使设计者实现不同时钟域之间的频率匹配。

面积和成本

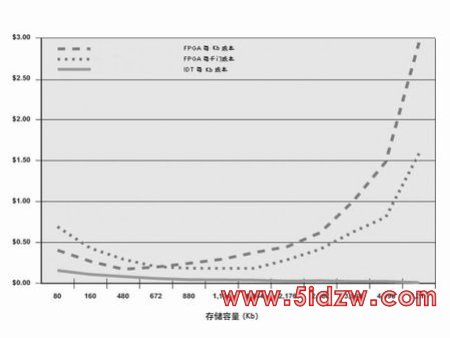

在设计缓冲器时,器件成本和板卡空间也是要考虑的因素。通过分析FIFO和FPGA 中存储器相关的单位比特成本,可以看出两种技术中的存储器成本在达到256K之前保持在非常相似的水平(见图3)。然而,FIFO 中的单位比特成本是随着密度的增加而稳定下降的,但是 FPGA 中存储器成本的增速很快。密度为 1 Mb 以上的 FPGA 存储器就变得过于昂贵了。

这种成本差异是非常令人吃惊的。当设计师被迫在 FPGA 设计中添加更多数量的存储器时,他们必须支付额外的存储器和嵌入到更高密度器件中的额外逻辑的成本。采用分立的 FIFO则可以稳定地增加密度。

封装面积和引脚也是需要考虑的重要内容。在低密度情况下,把缓冲器集成到单个 FPGA中可以实现更紧凑的引脚布局。然而,随着 FPGA密度和引脚数量的增加,这种折衷的效果并不明显。用大型的 8 M 门 FPGA 实现数据缓冲器需要设计师在电路板上焊接一个 1152 引脚 的 BGA,另一方面,不论存储器密度如何,采用比较简单的 256 引脚 BGA封装的FIFO即可达到相同的效果。

结语

随着数据速率的持续上升,数据缓冲器设计将在优化网络性能方面扮演重要的角色。通过分析所有的设计选择,并利用现成的分立器件和可编程逻辑器件的独特性能,设计师可以用尽可能低的成本构建高性能的解决方案。

,高端路由器设计需要考虑的数据缓冲器问题

异步设计中的时钟同步也是一个应该考虑的问题。在大多数路由器环境中,进入系统的传输线路与主系统时钟会在不同的时钟域中运行。设计师必须连接不同宽度的总线。路由器设计师面临的一个常见的挑战就是如何使用数据缓冲器使这些全异时钟同步,并复用16 位和 32 位或 32 位和 64 位之间的数据,以确保整个系统中数据的完整性。

设计师使用基于FPGA的方法调整他们的逻辑以实现上述目标。然而在一般情况下,该工作需要丰富的电路设计专业知识以及模拟和测试这些电路的时间。相比之下,许多高性能 FIFO 提供的嵌入式总线匹配能力可自动解决这个问题。这些器件可提供多总线宽度和端口可选的总线宽度匹配,有助于出口线路和入口线路之间的无缝连接。这些器件也具备独立的读写时钟,可使设计者实现不同时钟域之间的频率匹配。

面积和成本

在设计缓冲器时,器件成本和板卡空间也是要考虑的因素。通过分析FIFO和FPGA 中存储器相关的单位比特成本,可以看出两种技术中的存储器成本在达到256K之前保持在非常相似的水平(见图3)。然而,FIFO 中的单位比特成本是随着密度的增加而稳定下降的,但是 FPGA 中存储器成本的增速很快。密度为 1 Mb 以上的 FPGA 存储器就变得过于昂贵了。

图3 FPGA和分立FIFO方案的成本对比 |

封装面积和引脚也是需要考虑的重要内容。在低密度情况下,把缓冲器集成到单个 FPGA中可以实现更紧凑的引脚布局。然而,随着 FPGA密度和引脚数量的增加,这种折衷的效果并不明显。用大型的 8 M 门 FPGA 实现数据缓冲器需要设计师在电路板上焊接一个 1152 引脚 的 BGA,另一方面,不论存储器密度如何,采用比较简单的 256 引脚 BGA封装的FIFO即可达到相同的效果。

结语

随着数据速率的持续上升,数据缓冲器设计将在优化网络性能方面扮演重要的角色。通过分析所有的设计选择,并利用现成的分立器件和可编程逻辑器件的独特性能,设计师可以用尽可能低的成本构建高性能的解决方案。

,高端路由器设计需要考虑的数据缓冲器问题