标签:电源电路,电路设计,http://www.5idzw.com

高速ADC采集系统电路设计的考虑及分析,http://www.5idzw.com

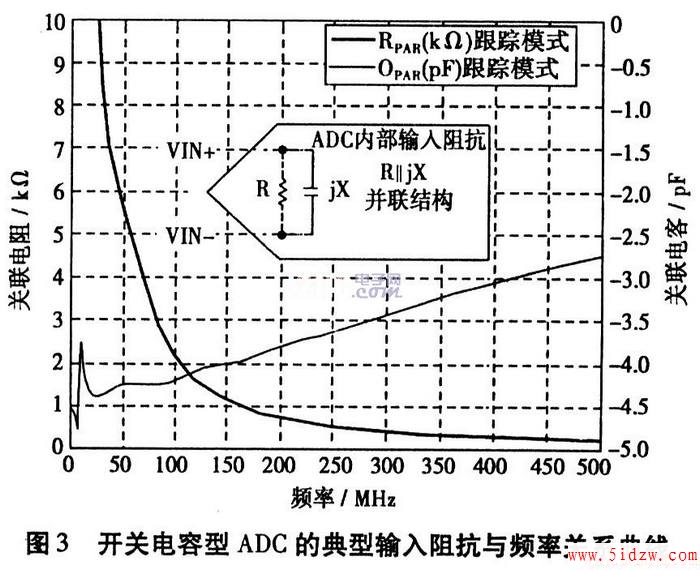

更为重要的是把外部网络阻抗与ADC跟踪模式阻抗匹配具有相当的难度,如图3所示,输入阻抗的实部或阻性阻抗(用蓝色线表示)在低频段(基带)非常高(在几千欧姆范围内),在超过100 MHz的频段下降到2 kΩ以下。输入阻抗的虚部或容性阻抗(用红色线表示),一开始从一个相当高的容性负载,然后在高频段减小大约3 pF。要匹配这样的输入阻抗是一个相当具有挑战性的设计问题,尤其是在频率高于100 MHz的情况下。